Something went wrong

An error has prevented the portal from working properly.

Please contact us .

You reached this page when trying to access MDI3MDQ5ZTAzYjcxLTcyNDgtZjNlNC03NDRiLWRhYzdkOTUy from 193.7.198.129 on April 28 2024, 08:00:29 UTC

A survey paper on design and implementation of multipliers for digital system applications

- Published: 20 January 2022

- Volume 55 , pages 4575–4603, ( 2022 )

Cite this article

- Srikanth Immareddy 1 &

- Aunmetha Sundaramoorthy 2

1460 Accesses

8 Citations

3 Altmetric

Explore all metrics

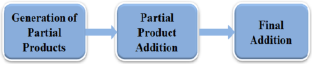

Multiplication is one of the essential functions in all digital systems. The evaluation of digital system, have brought out new challenges in VLSI (Very Large Scale Integration) designing. Multipliers are generally utilized in digital signal processing. Increasing technology has maximized the demand for rapid and efficient real-time digital signal processing applications. A huge number of multiplier designs have been developed for improving its speed. This manuscript provides an exploration of the different studies that have been conducted since 2015. This manuscript reviews investigation depends on various types of multipliers. A thorough statistical analysis is provided in this review which was conducted by extracting information from 100 papers published between the years 2015–2020. When comparing the adders, obtain the Ripple Carry Adder had lesser area while it had lower speed, in contrast to Carry Select Adders they are great speed but greater area. A Carry Look Ahead Adder sits among spectrum has a suitable balance among complexities of time and area. After designing and comparing the adders, turned to multipliers. At first opted for Parallel Multiplier and then Wallace Tree Multiplier. Meanwhile, learned the amount of delay was greatly decreased while Carry Save Adders were utilized on Wallace Tree applications. In this review, present the comparison and analysis of investigation manuscript depends on several criteria. In general, this manuscript summarizes the current state of knowledge of these multipliers. In this, the comparative analysis depends on timeline, reputation of simulation tools and types of device components are analyzed.

This is a preview of subscription content, log in via an institution to check access.

Access this article

Price includes VAT (Russian Federation)

Instant access to the full article PDF.

Rent this article via DeepDyve

Institutional subscriptions

Similar content being viewed by others

Design and Implementation of Adders and Multipliers for DSP Applications

Review on Different Types of Multipliers and Its Performance Comparisons

Implementation and Investigation of an Optimal Full Adder Design for Low Power and Reduced Delay Conditions

Data availability.

Data sharing is not applicable to this article as no new data were created or analyzed in this study.

Afzali-Kusha H, Vaeztourshizi M, Kamal M, Pedram M (2020) Design exploration of energy-efficient accuracy-configurable dadda multipliers with improved lifetime based on voltage overscaling. IEEE Trans Very Large Scale Integr (VLSI) Syst 28:1207–1220. https://doi.org/10.1109/tvlsi.2020.2978874

Article Google Scholar

Ahmed R, Thabah S, Saha P (2019) Design of new multi-column 5,5:4 compressor circuit based on double-gate UTBSOI transistors. Procedia Comput Sci 165:532–540. https://doi.org/10.1016/j.procs.2020.01.027

Alouani I, Ahangari H, Ozturk O, Niar S (2018) A novel heterogeneous approximate multiplier for low power and high performance. IEEE Embed Syst Lett 10:45–48. https://doi.org/10.1109/les.2017.2778341

Amanollahi S, Jaberipur G (2017) Fast energy efficient radix-16 sequential multiplier. IEEE Embed Syst Lett 9:73–76. https://doi.org/10.1109/les.2017.2714259

Ansari M, Jiang H, Cockburn B, Han J (2018) Low-power approximate multipliers using encoded partial products and approximate compressors. IEEE J Emerg Sel Topics Circuits Syst 8:404–416. https://doi.org/10.1109/jetcas.2018.2832204

Antelo E, Montuschi P, Nannarelli A (2017) Improved 64-bit radix-16 booth multiplier based on partial product array height reduction. IEEE Trans Circuits Syst I Regul Pap 64:409–418. https://doi.org/10.1109/tcsi.2016.2561518

Ariafar Z, Mosleh M (2019) Effective designs of reversible vedic multiplier. Int J Theor Phys 58:2556–2574. https://doi.org/10.1007/s10773-019-04145-0

Article MathSciNet MATH Google Scholar

Babu CN, Sai PN, Priyanka C, Kishore KH, Bhargavi MB, Karthik K (2018) Comparative analysis of high speed carry skip adders. Int J Eng Technol 7(2):121–125

Bahar A, Wahid K (2019) Design of QCA-serial parallel multiplier (QSPM) with energy dissipation analysis. IEEE Trans Circuits Syst II Express Briefs. https://doi.org/10.1109/tcsii.2019.2953866

Barik R, Pradhan M, Panda R (2017) Time efficient signed Vedic multiplier using redundant binary representation. J Eng 2017:60–68. https://doi.org/10.1049/joe.2016.0376

Basiri MM, Shukla S (2017) Flexible VLSI architectures for Galois field multipliers. Integration 59:109–124. https://doi.org/10.1016/j.vlsi.2017.06.009

Behl A, Gokhale A, Sharma N (2020) Design and implementation of fast booth-2 multiplier on artix FPGA. Procedia Comput Sci 173:140–148. https://doi.org/10.1016/j.procs.2020.06.018

Bhattacharjee D, Siemon A, Linn E, Chattopadhyay A (2017) Efficient complementary resistive switch-based crossbar array Booth multiplier. Microelectron J 64:78–85. https://doi.org/10.1016/j.mejo.2017.04.010

Boro B, Reddy K, Kumar Y, Vasantha M (2020) Approximate radix-8 booth multiplier for low power and high speed applications. Microelectron J 101:104816. https://doi.org/10.1016/j.mejo.2020.104816

Chang Y, Cheng Y, Liao S, Hsiao C (2020) A low power radix-4 booth multiplier with pre-encoded mechanism. IEEE Access 8:114842–114853. https://doi.org/10.1109/access.2020.3003684

Chen Y, Li C, Lai L (2017) Fine-tuning accuracy using conditional probability of the bottom sign-bit in fixed-width modified booth multiplier. Circuits Syst Signal Process 37:3115–3130. https://doi.org/10.1007/s00034-017-0702-7

Chiou C, Lee C, Lin J et al (2017) Low-latency digit-serial dual basis multiplier for lightweight cryptosystems. IET Inf Secur 11:301–311. https://doi.org/10.1049/iet-ifs.2015.0336

Chudasama A, Sasamal T, Yadav J (2018) An efficient design of Vedic multiplier using ripple carry adder in quantum-dot cellular automata. Comput Electr Eng 65:527–542. https://doi.org/10.1016/j.compeleceng.2017.09.019

Cui X, Dong W, Liu W et al (2017) High performance parallel decimal multipliers using hybrid BCD codes. IEEE Trans Comput 66:1994–2004. https://doi.org/10.1109/tc.2017.2706262

Del Barrio A, Hermida R, Ogrenci-Memik S (2019) A combined arithmetic-high-level synthesis SOLUTION to deploy partial carry-save radix-8 booth multipliers in datapaths. IEEE Trans Circuits Syst I Regul Pap 66:742–755. https://doi.org/10.1109/tcsi.2018.2866172

Diaz C, Frias T, Sanchez G et al (2017) A novel parallel multiplier using spiking neural P systems with dendritic delays. Neurocomputing 239:113–121. https://doi.org/10.1016/j.neucom.2017.02.009

Edrisi Arani I, Rezai A (2018) Novel circuit design of serial–parallel multiplier in quantum-dot cellular automata technology. J Comput Electron 17:1771–1779. https://doi.org/10.1007/s10825-018-1220-y

Ernest Ravindran RS, Priyadarshini KM, Sai AT, Shiny P, Sabeena S (2019) Design of finite field multiplier for efficient data encryption. Int J Adv Sci Technol 28(20):42–52

Google Scholar

Esmali Nojehdeh M, Altun M (2020) Systematic synthesis of approximate adders and multipliers with accurate error calculations. Integration 70:99–107. https://doi.org/10.1016/j.vlsi.2019.10.001

Esposito D, Strollo A, Napoli E et al (2018) Approximate multipliers based on new approximate compressors. IEEE Trans Circuits Syst I Regul Pap 65:4169–4182. https://doi.org/10.1109/tcsi.2018.2839266

Faraone J, Kumm M, Hardieck M, Zipf P, Liu X, Boland D, Leong PH (2019) Addnet: deep neural networks using fpga-optimized multipliers. IEEE Trans Very Large Scale Integr (VLSI) Syst 28(1):115–28

Farrukh F, Zhang C, Jiang Y et al (2020) Power efficient tiny yolo CNN using reduced hardware resources based on booth multiplier and WALLACE tree adders. IEEE Open J Circuits Syst. https://doi.org/10.1109/ojcas.2020.3007334

Fritz C, Fam A (2016) Interlaced partition multiplier. IEEE Trans Comput 65:2672–2677. https://doi.org/10.1109/tc.2015.2481379

Frustaci F, Perri S, Corsonello P, Alioto M (2020) Approximate multipliers with dynamic truncation for energy reduction via graceful quality degradation. IEEE Trans Circuits Syst II Express Briefs. https://doi.org/10.1109/tcsii.2020.2999131

Gudivada A, Sudha G (2020) Design of Baugh-Wooley multiplier in quantum-dot cellular automata using a novel 1-bit full adder with power dissipation analysis. SN Appl Sci. https://doi.org/10.1007/s42452-020-2595-5

Gupta T, Sharma J (2018) Han-Carlson adder based high-speed Vedic multiplier for complex multiplication. Microsyst Technol 24:3901–3906. https://doi.org/10.1007/s00542-018-3872-8

Ha M, Lee S (2018) Multipliers with approximate 4–2 compressors and error recovery modules. IEEE Embed Syst Lett 10:6–9. https://doi.org/10.1109/les.2017.2746084

Haridas G, George D (2016) Area efficient low power modified booth multiplier for FIR filter. Procedia Technol 24:1163–1169. https://doi.org/10.1016/j.protcy.2016.05.070

Hashemi Namin S, Wu H, Ahmadi M (2017) Low-power design for a digit-Serial Polynomial basis finite field multiplier using factoring technique. IEEE Trans Very Large Scale Integr (VLSI) Systems 25:441–449. https://doi.org/10.1109/tvlsi.2016.2585980

He Y, Yang J, Chang C (2017) Design and evaluation of booth-encoded multipliers in redundant binary representation. Embedded Syst Des Spec Arith Number Syst. https://doi.org/10.1007/978-3-319-49742-6_6

He Y, Yi X, Zhang Z et al (2020) A probabilistic prediction-based fixed-width booth multiplier for approximate computing. IEEE Trans Circuits Syst I Regul Pap. https://doi.org/10.1109/tcsi.2020.3001654

Hosseinzadeh Namin P, Roma C, Muscedere R, Ahmadi M (2018) Efficient VLSI implementation of a sequential finite field multiplier using reordered normal basis in domino logic. IEEE Trans Very Large Scale Integr (VLSI) Systems 26:2542–2552. https://doi.org/10.1109/tvlsi.2018.2851958

Imana J (2018) Fast bit-parallel binary multipliers based on type-I pentanomials. IEEE Trans Comput 67:898–904. https://doi.org/10.1109/tc.2017.2778730

Imana J (2020) LFSR-based bit-serial $GF(2^m)$ multipliers using irreducible trinomials. IEEE Trans Comput. https://doi.org/10.1109/tc.2020.2980259

Javadi M, Yalame M, Mahdiani H (2020) Small constant mean-error imprecise adder/multiplier for efficient VLSI implementation of MAC-based applications. IEEE Trans Comput 69:1376–1387. https://doi.org/10.1109/tc.2020.2972549

Jiang H, Han J, Qiao F, Lombardi F (2016) Approximate radix-8 booth multipliers for low-power and high-performance operation. IEEE Trans Comput 65:2638–2644. https://doi.org/10.1109/tc.2015.2493547

Jiang H, Liu C, Lombardi F, Han J (2019a) Low-power approximate unsigned multipliers with configurable error recovery. IEEE Trans Circuits Syst I Regul Pap 66:189–202. https://doi.org/10.1109/tcsi.2018.2856245

Jiang H, Liu L, Jonker P et al (2019b) A high-performance and energy-EFFICIENT FIR adaptive filter using approximate distributed arithmetic circuits. IEEE Trans Circuits Syst I Regul Pap 66:313–326. https://doi.org/10.1109/tcsi.2018.2856513

Karunakaran S, Gattim NK (2019) VLSI implementation of folded FIR filter structures using high speed multipliers. J Eng Appl Sci 14(4):1070–1077

Kavitha M, Rangarajan P (2020) An efficient FPGA architecture for reconfigurable FFT processor incorporating an integration of an improved CORDIC and radix-2r algorithm. Circuits Syst Signal Process 39:5801–5829. https://doi.org/10.1007/s00034-020-01436-4

Kivi Sona M, Somasundaram V (2020) Vedic multiplier implementation in VLSI. Mater Today Proc 24:2219–2230. https://doi.org/10.1016/j.matpr.2020.03.748

Kumar MS, Tulasi SK, Srinivasulu N, Bandi VL, Kishore KH (2018) Bit wise and delay of vedic multiplier. Int J Eng Technol (UAE) 7(1.5):26–30

Lee C, Meher P, Liu C (2016) Area-delay efficient digit-serial multiplier based on -partitioning scheme combined with TMVP block recombination approach. IEEE Trans Very Large Scale Integr (VLSI) Syst 24:2413–2425. https://doi.org/10.1109/tvlsi.2016.2514272

Lee T, Liu M, Huang C et al (2019) Design of a digit-serial multiplier over GF(2m) using a karatsuba algorithm. J Chin Inst Eng 42:602–612. https://doi.org/10.1080/02533839.2019.1644200

Leon V, Zervakis G, Soudris D, Pekmestzi K (2018) Approximate hybrid high radix encoding for energy-efficient inexact multipliers. IEEE Trans Very Large Scale Integr (VLSI) Syst 26:421–430. https://doi.org/10.1109/tvlsi.2017.2767858

Leon V, Xydis S, Soudris D, Pekmestzi K (2019) Energy-efficient VLSI implementation of multipliers with double LSB operands. IET Circuits Devices Syst 13:816–821. https://doi.org/10.1049/iet-cds.2018.5039

Liang S, Yin S, Liu L, Luk W, Wei S (2018) FP-BNN: binarized neural network on FPGA. Neurocomputing 275:1072–86

Liu W, Qian L, Wang C et al (2017) Design of approximate radix-4 booth multipliers for error-tolerant computing. IEEE Trans Comput 66:1435–1441. https://doi.org/10.1109/tc.2017.2672976

Liu W, Zhang T, McLarnon E et al (2019) Design and analysis of majority logic based approximate adders and multipliers. IEEE Trans Emerg Top Comput. https://doi.org/10.1109/tetc.2019.2929100

Mahmoud M, El-Dib D, Fahmy H (2017) Low energy pipelined dual base (decimal/binary) multiplier, DBM, design. Microelectron J 65:11–20. https://doi.org/10.1016/j.mejo.2017.05.004

Marimuthu R, Rezinold Y, Mallick P (2017) Design and analysis of multiplier using approximate 15–4 compressor. IEEE Access 5:1027–1036. https://doi.org/10.1109/access.2016.2636128

Mariya Priyadarshini K, Ernest Ravindran RS, Atindra Chandra Sekhar M, Sai Kalyan PJV, Rahul G (2019) A high-speed precision-controllable approximate 16 bit multiplier. Int J Adv Sci Technol 28(20):31–41

Mazahir S, Hasan O, Hafiz R, Shafique M (2017) Probabilistic error analysis of approximate recursive multipliers. IEEE Trans Comput 66:1982–1990. https://doi.org/10.1109/tc.2017.2709542

Mittal S (2020) A survey of FPGA-based accelerators for convolutional neural networks. Neural Comput Appl 32(4):1109–1139

Mohanty B, Choubey A (2016) Efficient design for radix-8 booth multiplier and its application in lifting 2-D DWT. Circuits Syst Signal Process 36:1129–1149. https://doi.org/10.1007/s00034-016-0349-9

Moss D, Boland D, Leong P (2019) A two-speed, radix-4, serial-parallel multiplier. IEEE Trans Very Large Scale Integr (VLSI) Syst 27:769–777. https://doi.org/10.1109/tvlsi.2018.2883645

Mrazek V, Vasicek Z, Sekanina L et al (2018) Scalable construction of approximate multipliers with formally guaranteed worst case error. IEEE Trans Very Large Scale Integr (VLSI) Syst 26:2572–2576. https://doi.org/10.1109/tvlsi.2018.2856362

Mrazek V, Sekanina L, Vasicek Z (2020) Using libraries of approximate circuits in design of hardware accelerators of deep neural networks. In 2020 2nd IEEE international conference on artificial intelligence circuits and systems (AICAS). IEEE. pp. 243–247

Mythili S, Thiyagarajah K, Rajesh P, Shajin FH (2020) Ideal position and size selection of unified power flow controllers (UPFCs) to upgrade the dynamic stability of systems: an antlion optimiser and invasive weed optimisation algorithm. HKIE Trans 27(1):25–37

Patali P, Thottathikkulam Kassim S (2020) Efficient modular hybrid adders and radix-4 booth multipliers for DSP applications. Microelectron J 96:104701. https://doi.org/10.1016/j.mejo.2020.104701

Periyasamy M, Gandhi M, Sakthivel B, Murugeswari S (2020) A novel fault tolerant multiplier using single digit conversion based self checking scheme. Mater Today Proc. https://doi.org/10.1016/j.matpr.2020.03.204

Perri S, Spagnolo F, Frustaci F, Corsonello P (2020) Parallel architecture of power-of-two multipliers for FPGAs. IET Circuits Devices Syst 14:381–389. https://doi.org/10.1049/iet-cds.2019.0246

Pilipovic R, Bulic P (2020) On the design of logarithmic multiplier using radix-4 booth encoding. IEEE Access 8:64578–64590. https://doi.org/10.1109/access.2020.2985345

Pilipović R, Bulić P (2020) On the design of logarithmic multiplier using radix-4 booth encoding. IEEE Access 8:64578–64590

Pillutla S, Boppana L (2020a) An area-efficient bit-serial sequential polynomial basis finite field GF(2) multiplier. AEU-Int J Electron C 114:153017. https://doi.org/10.1016/j.aeue.2019.153017

Pillutla S, Boppana L (2020b) Area-efficient low-latency polynomial basis finite field GF(2) systolic multiplier for a class of trinomials. Microelectron J 97:104709. https://doi.org/10.1016/j.mejo.2020.104709

Prabhu E, Mangalam H, Gokul P (2018) A delay efficient vedic multiplier. Proc Natl Acad Sci India Sect A Phys Sci 89:257–268. https://doi.org/10.1007/s40010-017-0464-4

Praveen Kumar Y, Kariyappa B, Shashank S, Bharath C (2020) Performance analysis of multipliers using modified gate diffused input technology. IETE J Res. https://doi.org/10.1080/03772063.2020.1782778

Priyadarshini KM, Ravindran RSE, Bhaskar PR (2019) A detailed scrutiny and reasoning on VLSI binary adder circuits and architectures. Int J Innov Technol Explor Eng 8(7):887–895

Priyanka C, Pratap ER, Bhaskar S, Naresh Y (2019) An optimized area efficient high speed CSD multiplier for image processing applications. Int J Innov Technol Explor Eng 8(7):1384–1388

Qiqieh I, Shafik R, Tarawneh G et al (2018) Significance-driven logic compression for energy-efficient multiplier design. IEEE J Emerg Sel Topics Circuits Syst 8:417–430. https://doi.org/10.1109/jetcas.2018.2846410

Radakovits D, TaheriNejad N, Cai M et al (2020) A memristive multiplier using semi-serial IMPLY-based adder. IEEE Trans Circuits Syst I Regul Pap 67:1495–1506. https://doi.org/10.1109/tcsi.2020.2965935

Rajesh P, Shajin F (2020) A multi-objective hybrid algorithm for planning electrical distribution system. Eur J Electrical Eng 22(4–5):224–509

Rajput R, Swamy M (2016) Superscalar pipelined inner product computation unit for signed unsigned number. Perspect Sci 8:606–610. https://doi.org/10.1016/j.pisc.2016.06.034

Reddy PS, Satyanarayana P, Krishna GS, Divya K (2018) Hardware implementation of variable digital filter using constant coefficient multiplier for SDR applications. Artificial intelligence and evolutionary computations in engineering systems. Springer, Singapore, pp 495–502

Chapter Google Scholar

Reddy KM, Vasantha MH, Kumar YN, Dwivedi D (2019) Design and analysis of multiplier using approximate 4–2 compressor. AEU-Int J Electron Commun 107:89–97

Roy A, Dhar A (2020) SIBAM-sign inclusive broken array multiplier design for error tolerant applications. IEEE Trans Circuits Syst II Express Briefs. https://doi.org/10.1109/tcsii.2020.2969903

Sabetzadeh F, Moaiyeri M, Ahmadinejad M (2019) A majority-based imprecise multiplier for ultra-efficient approximate image multiplication. IEEE Trans Circuits Syst I Regul Pap 66:4200–4208. https://doi.org/10.1109/tcsi.2019.2918241

Sakellariou P, Paliouras V (2016) Application-specific low-power multipliers. IEEE Trans Comput 65:2973–2985. https://doi.org/10.1109/tc.2016.2516016

Savadi A, Yanamshetti R, Biradar S (2016) Design and implementation of 64 bit IIR filters using vedic multipliers. Procedia Comput Sci 85:790–797. https://doi.org/10.1016/j.procs.2016.05.267

Shajin F, Rajesh P (2020) Trusted secure geographic routing protocol: outsider attack detection in mobile ad hoc networks by adopting trusted secure geographic routing protocol. Int J Pervasive Comput Commun. https://doi.org/10.1108/IJPCC-09-2020-0136

Shanmuganathan R, Brindhadevi K (2019) Comparative analysis of various types of multipliers for effective low power. Microelectron Eng 214:28–37. https://doi.org/10.1016/j.mee.2019.04.015

Shao B, Li P (2015) Array-based approximate arithmetic computing: a general model and applications to multiplier and squarer design. IEEE Trans Circuits Syst I Regul Pap 62:1081–1090. https://doi.org/10.1109/tcsi.2015.2388839

Shukla V, Singh O, Mishra G, Tiwari R (2020) Design of array multiplier circuit using reversible logic approach with optimized performance parameters. Smart Healthc Dis Diagnosis Prev. https://doi.org/10.1016/b978-0-12-817913-0.00013-4

Singh P, Neema V, Daulatabad S, Shah A (2016) Subthreshold circuit designing and implementation of finite field multiplier for cryptography application. Procedia Comput Sci 79:597–602. https://doi.org/10.1016/j.procs.2016.03.075

Siva Kumar M, Tulasi SK, Karanam S, Tejdeep P, Nagarjuna A, Srisairajvenkat K (2017) A novel low power and low delay buffer using domino logic design in 32 nm technology. J Theor Appl Inf Technol 95(10):2132–2138

Soumya N, Sai Kumar K, Raghava Rao K, Rooban S, Sampath Kuma RP, Santhosh Kumar GN (2019) 4-bit multiplier design using cmos gates in electric VLSI. Int J Recent Technol Eng 8(2):1172–1177

Stoeva D, Balazs P (2020) A survey on the unconditional convergence and the invertibility of frame multipliers with implementation. Sampling theory and applications. Springer, Cham, pp 169–192

Strollo A, Napoli E, De Caro D et al (2020) Comparison and extension of approximate 4–2 compressors for low-power approximate multipliers. IEEE Trans Circuits Syst I Regul Pap. https://doi.org/10.1109/tcsi.2020.2988353

Subathradevi S, Vennila C (2018) Systolic array multiplier for augmenting data center networks communication link. Clust Comput 22:13773–13783. https://doi.org/10.1007/s10586-018-2092-4

Sundhari MR (2019) An efficient implementation of low-power approximate compressor-based multiplier for cognitive communication systems. Int J Commun Syst. https://doi.org/10.1002/dac.4180

Thota MK, Shajin FH, Rajesh P (2020) Survey on software defect prediction techniques. Int J Appl Sci Eng 17:331–344

Ullah S, Rehman S, Shafique M, Kumar A (2021) High-performance accurate and approximate multipliers for FPGA-based hardware accelerators. IEEE Trans Comput-Aided Des Integr Circuits Syst. https://doi.org/10.1109/TCAD.2021.3056337

Valinataj M (2017) Novel parity-preserving reversible logic array multipliers. J Supercomput 73:4843–4867. https://doi.org/10.1007/s11227-017-2057-z

Van Toan N, Lee J (2020) FPGA-based multi-level approximate multipliers for high-performance error-resilient applications. IEEE Access 8:25481–25497. https://doi.org/10.1109/access.2020.2970968

Venkatachalam S, Ko S (2017) Design of power and area efficient approximate multipliers. IEEE Trans Very Large Scale Integr (VLSI) Syst 25:1782–1786. https://doi.org/10.1109/tvlsi.2016.2643639

Venkatachalam S, Adams E, Lee H, Ko S (2019) Design and analysis of area and power efficient approximate booth multipliers. IEEE Trans Comput 68:1697–1703. https://doi.org/10.1109/tc.2019.2926275

Véstias M, Neto H (2018) Improving the area of fast parallel decimal multipliers. Microprocess Microsyst 61:96–107. https://doi.org/10.1016/j.micpro.2018.05.015

Waris H, Wang C, Liu W (2020) Hybrid low radix encoding based approximate booth multipliers. IEEE Trans Circuits Syst II Express Briefs. https://doi.org/10.1109/tcsii.2020.2975094

Xie J, Lee C, Meher P, Mao Z (2019) Novel bit-parallel and digit-serial systolic finite field multipliers over $GF(2^m)$ based on reordered normal basis. IEEE Trans Very Large Scale Integr (VLSI) Syst 27:2119–2130. https://doi.org/10.1109/tvlsi.2019.2918836

Xue H, Patel R, Boppana N, Ren S (2018) Low-power-delay-product radix-4 8*8 booth multiplier in CMOS. Electron Lett 54:344–346. https://doi.org/10.1049/el.2017.3996

Yan W, Ercegovac M, Chen H (2016) An energy-efficient multiplier with fully overlapped partial products reduction and final addition. IEEE Trans Circuits Syst I Regul Pap 63:1954–1963. https://doi.org/10.1109/tcsi.2016.2600159

Yan J, Guo F, Wen C, Li G (2020) Parallel alternating direction method of multipliers. Inf Sci 507:185–196. https://doi.org/10.1016/j.ins.2019.08.039

Ye J, Shieh M (2018) Low-complexity VLSI design of large integer multipliers for fully homomorphic encryption. IEEE Trans Very Large Scale Integr (VLSI) Syst 26:1727–1736. https://doi.org/10.1109/tvlsi.2018.2829539

Yin P, Wang C, Waris H et al (2020) Design and analysis of energy-efficient dynamic range approximate logarithmic multipliers for machine learning. IEEE Trans Sustain Comput. https://doi.org/10.1109/tsusc.2020.3004980

Download references

No funding has been received. The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

Author information

Authors and affiliations.

Department of Electronics and Communication Engineering, Koneru Lakshmiah Education Foundation, Vaddeswaram, Andhra Pradesh, India, 522 501

Srikanth Immareddy

Aunmetha Sundaramoorthy

You can also search for this author in PubMed Google Scholar

Corresponding author

Correspondence to Srikanth Immareddy .

Ethics declarations

Conflict of interest.

Authors declare that they have no conflict of interest.

Ethical approval

This article does not contain any studies with human participants performed by any of the authors.

Additional information

Publisher's note.

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Reprints and permissions

About this article

Immareddy, S., Sundaramoorthy, A. A survey paper on design and implementation of multipliers for digital system applications. Artif Intell Rev 55 , 4575–4603 (2022). https://doi.org/10.1007/s10462-021-10113-0

Download citation

Accepted : 01 December 2021

Published : 20 January 2022

Issue Date : August 2022

DOI : https://doi.org/10.1007/s10462-021-10113-0

Share this article

Anyone you share the following link with will be able to read this content:

Sorry, a shareable link is not currently available for this article.

Provided by the Springer Nature SharedIt content-sharing initiative

- Very large scale integration

- Multipliers

- Digital signal processing (DSP)

- Parallel multiplier

- Carry save adders

- Carry look ahead adder

- Find a journal

- Publish with us

- Track your research

Medical applications of DSP

Ieee account.

- Change Username/Password

- Update Address

Purchase Details

- Payment Options

- Order History

- View Purchased Documents

Profile Information

- Communications Preferences

- Profession and Education

- Technical Interests

- US & Canada: +1 800 678 4333

- Worldwide: +1 732 981 0060

- Contact & Support

- About IEEE Xplore

- Accessibility

- Terms of Use

- Nondiscrimination Policy

- Privacy & Opting Out of Cookies

A not-for-profit organization, IEEE is the world's largest technical professional organization dedicated to advancing technology for the benefit of humanity. © Copyright 2024 IEEE - All rights reserved. Use of this web site signifies your agreement to the terms and conditions.

IMAGES

VIDEO

COMMENTS

The journal disseminates impactful and re-usable scientific software through Original Software Publications which describe the application of the software to research and the published outputs. For more information contact us at: [email protected]. Digital Signal Processing: A Review Journal is one of the oldest and most established ...

Dear Colleagues, Research on digital signal processing offers a variety of applications that range from the entertainment (music) industry to banking (economy). The next entertainment era is expected to have fully automated tools for music composition, where audio/signal processing is crucial. Regarding financing, most deals are agreed upon ...

Conclusion. In the field of communication, the application of digital signal process ing technology is mainly. manifested in speech compression coding and software radio. Although its advantages ...

Paper • The following article is Open access. Research on Application of Digital Signal Processing Technology in Communication. Huang Lu1, Yuan Xiaoyu1, Wang Haodong1, Li Jin1, Ma Xuejiao1 and Zhang Caihong1. Published under licence by IOP Publishing Ltd IOP Conference Series: Materials Science and Engineering , Volume 799 , International ...

Abstract and Figures. Digital Signal Processing (DSP) is the use of digital processing systems by computers in order to perform a variety of signal processing operations. It is the mathematical ...

Abstract—Digital Signal Processing (DSP) is the use of digital processing systems by computers in order to perform a variety of signal processing operations. It is the mathematical manipulation of a digital signal's numerical values in order to increase quality as well as effects of signals. DSP can include linear or nonlinear operators in

This special issue (SI) encourages to present research achievement of new theories and methods of signal processing the researchers develop. Digital signal processing (DSP) is the use of digital processing, such as by computers or more specialized digital signal processors, to perform a wide variety of signal processing operations.

For general information on our other products and services please contact our Customer Care Department with the U.S. at 877-762-2974, outside the U.S. at 317-572-3993 or fax 317-572-4002. Wiley also publishes its books in a variety of electronic formats.

In the future, digital signal processing will develop towards the research of fast and efficient algorithms, high-speed hardware implementation, and new application research. This Special Issue focuses on the application of digital signal processing algorithms to future digital communication systems to help the reader clarify the motivations ...

digital system, have brought out new challenges in VLSI (Very Large Scale Integration) designing. Multipliers are generally utilized in digital signal processing. Increasing tech-nology has maximized the demand for rapid and ecient real-time digital signal process-ing applications. A huge number of multiplier designs have been developed for ...

This chapter contains sections titled: DTMF Signal Detection Using Correlation, FFT, and Goertzel Algorithm Beat Detection Using Onboard LEDs FIR with RTD DSP Applications and Student Projects | part of Digital Signal Processing and Applications with the TMS320C6713 and TMS320C6416 DSK | Wiley-IEEE Press books | IEEE Xplore

Abstract: Research in graph signal processing (GSP) aims to develop tools for processing data defined on irregular graph domains. In this paper, we first provide an overview of core ideas in GSP and their connection to conventional digital signal processing, along with a brief historical perspective to highlight how concepts recently developed in GSP build on top of prior research in other areas.

In this paper, the uses and functions of an existing, widely available digital signal processor (DSP) is extended to include using it to generate needed waveforms that could be used for computing, filtering, modulation and noise removal applications at the edges of communication networks that supports Industrial Internet of Things (IIoT) and Cyber Physical Systems (CPS). Such waveforms could ...

1 Introduction. Digital signal processing technology, as an important product of the information age, exists in all aspects of the communication field and is an indispensable technology in the communication field. In recent years, China has increased its support for chips. Therefore, it has promoted the development and promotion of DSP chips ...

digital signal processing technology in the communication field, and the specific applications of speech compression coding and software radio in communication are analyzed in order to better

The engineering applications of Digital Signal Processing (DSP) are vast and may be said to be a fundamental aspect of our "Digital Society". Today, many aspects of electrical and electronic engineering are essentially applications of DSP. This is because of the focus on processing information in the form of digital signals using specialist ...

A Feature Paper should be a substantial original Article that involves several techniques or approaches, provides an outlook for future research directions and describes possible research applications. Feature papers are submitted upon individual invitation or recommendation by the scientific editors and must receive positive feedback from the ...

Markets have always influenced the central thrust of the semiconductor industry. Beginning in the early eighties, the personal computer (PC) market has been the dominant market influencing the semiconductor industry. Single-chip microprocessors (MPUs) enabled what became the huge PC market, which ultimately overshadowed the earlier minicomputer and mainframe computer markets. The popularity of ...

The advantages and disadvantages of digital signal processing technology in the communication field, and the specific applications of speech compression coding and software radio in communication are analyzed are analyzed in order to better promote the application of digital Signal Processing Technology in the Communication field. With the continuous development of modern information ...

Research on Application of Digital Signal Processing. Technology in Communication. Huang Lu, Yuan Xiaoyu, Wang Haod ong, Li Jin, Ma Xuejiao, Zhang Caihong*. Qinghai Normal University, Xi 'ning ...

signal into another according to some fixed set of rules or equations. A digital signal processing, receives an electrical signal of microsecond duration, for example, representing the data, extracts the data from the signal, sends it to the output, and then goes back to repeat the process. This is the general nature of our technology today.

This paper describes the applications of Matlab in signals and. systems and digital signal processing DSP. Matlab provide. various methods to analyze the signals and systems, including. both ...

Biomedicine represents an important and very fertile area both for the application of conventional digital signal processing (DSP) techniques and the development of new and robust DSP algorithms. Signal processing, in various forms, is at the core of a large number of medical equipment today, and it continues to play a crucial role in the analysis of medical data. Some of the key aspects of ...